## Hydrogen Defect Passivation of Silicon Transistor on Plastic for High Performance Flexible Device Application

Musarrat Hasan,<sup>a,z</sup> Sun Jin Yun,<sup>a</sup> Jae Bon Koo,<sup>a</sup> Sang Hee Ko Park,<sup>a</sup> Yong Hae Kim,<sup>a</sup> Seung Youl Kang,<sup>a</sup> Jonghyun Rho,<sup>b</sup> Jee Hoon Kim,<sup>b</sup> Houk Jang,<sup>b</sup> Jong-Hyun Ahn,<sup>b,z</sup> Min-Seok Jo,<sup>c</sup> and Hyunsang Hwang<sup>c</sup>

<sup>a</sup>New Devices and Materials Research Department, Electronics and Telecommunication Research Institute, Daejeon 305-700, Korea

<sup>b</sup>School of Advanced Materials Science and Engineering, SKKU Advanced Institute of Nanotechnology, Sungkyunkwan University, Suwon 440-746, Korea

<sup>c</sup>Materials Science and Engineering Department, Gwangju Institute of Science and Technology, Gwangju 500-712, Korea

The electrical characteristics of a transistor on a transferred silicon ribbon are demonstrated. The process temperature is limited to 200°C for potential use on plastic sheets. Additional hydrogen annealing reduces the threshold voltage and improves the transistor properties. A high mobility of around 160 cm<sup>2</sup>/V s, with a high on/off ratio and an off current of as low as  $<10^{11}$  A, is achieved. The flexibility of the device is evaluated after applying stress in the bended condition. The device shows very little change in properties with a bending radius <4 mm. Overall, good electrical and mechanical properties are demonstrated for future use on flexible device applications.

© 2009 The Electrochemical Society. [DOI: 10.1149/1.3276689] All rights reserved.

Manuscript submitted October 18, 2009; revised manuscript received December 1, 2009. Published December 29, 2009.

Electronic devices on a flexible plastic substrate soon have a market potential in the form of flexible displays, radio frequency identification tags, solar cells, and various biosystems.<sup>1,2</sup> Many organic semiconductors,<sup>3,4</sup> oxide semiconductors,<sup>5,6</sup> and amorphous and polysilicon<sup>7,8</sup> have been used as an active semiconductor layer for a flexible device application. But due to their intrinsic limitations, it is not possible to obtain high performance devices. Hence, there is no alternative but to use a single-crystal semiconductor as an active layer. Mietl et al.,<sup>9</sup> Menard et al.,<sup>10</sup> and Ahn et al.<sup>11</sup> developed a transfer technique where after the doping process, a single crystalline silicon active layer can be transferred onto the plastic sheet from the silicon-on-insulator (SOI) wafers, which is quite attractive for a high performance transistor.

The dielectric grown at low temperatures on the plastic sheets contains many defect sites and interface dangling bonds.<sup>12,13</sup> To improve the device properties, successful defect passivation is absolutely necessary. Hydrogen (H<sub>2</sub>) passivates the defect sites far more effectively, especially near the interface region.<sup>14,15</sup> Some studies also show effective passivation even at relatively lower temperatures.<sup>16-18</sup> In this study, transistor properties with an aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) gate dielectric and platinum (Pt) as a gate electrode are presented. Properties in the bended condition are also reported.

After defining the doping region on the SOI wafer, the phosphorous spin-on-dopant (P509) was used for convenience.<sup>19</sup> The doping concentration was measured to be  $2 \times 10^{18}$  cm<sup>-3</sup> after activation annealing at 950°C. After etching the underneath SiO<sub>2</sub> layer, 290 nm of the top Si layer can be transferred onto the polyimide (PI) sheet via the poly(dimethylsiloxane) stamping process. A detailed transfer process has been described elsewhere.<sup>11</sup> After the transfer process, Al<sub>2</sub>O<sub>3</sub> was deposited as a gate dielectric in a plasmaenhanced atomic layer deposition chamber at 200°C. The thickness of the dielectric was  $\sim$  77 nm and that of the dielectric constant was 7.8 nm. After the source-drain gate patterning, platinum of  $\sim 100$  nm thickness was deposited as an electrode, and a lift-off process was adopted. Figure 1a shows the schematic cross-sectional view of the top-gate device structure on the PI sheet. The device width was 200 µm with the channel length varied from 10 to 20 µm. To improve the contact between the metal and sourcedrain, a forming gas annealing (FGA) process ( $H_2 = 3$  wt % and the rest is N<sub>2</sub>) was performed at 200°C at 1 atm pressure for 1 h.

Consequently, high pressure pure  $H_2$  annealing (HPHA, 20 atm, 99.99%) was also performed at 200°C. A computer-controlled bending test module was used for the bending test of the PI sheet.

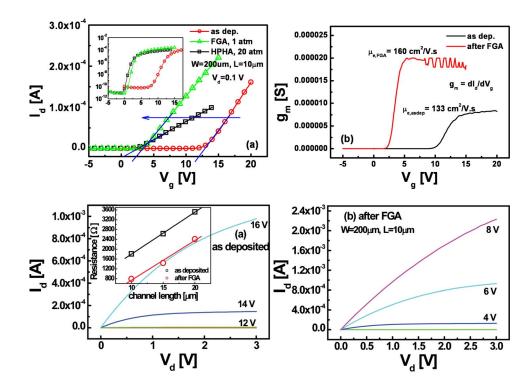

Figure 1b shows the device at a compressive stress condition on the bending stage. Figure 1c shows the transfer  $(I_d-V_g)$  characteristic of the as-deposited sample both in the linear and log scale. The  $I_d-V_g$ curve shows the typical n-type transistor with an enhancement mode of operation. The linear scale shows the threshold voltage  $(V_{th})$  of +10.8 V, which is quite high, indicating many charges and defects at the dielectric and interfaces. To reduce  $V_{th}$  and improve the interface, an additional annealing step in forming gas and H<sub>2</sub> was performed. The transfer curve is shown in Fig. 2a, in both the linear and log scale (the inset). As indicated by the arrows,  $V_{th}$  significantly reduced to 2.2 V after FGA and to 0.5 V after HPHA. The off current reduced to below  $10^{-11}$  A with little change in the on current. The result can be related to the better contact between the metal and the dielectric and also the defect passivation by H<sub>2</sub> near the interface and bulk oxide.

Figure 2b compares the transconductance values between both the as-deposited and FGA samples. After FGA, the  $g_m$  peak value increased from 8 to 20  $\mu$ S. The corresponding effective peak mobilities for the FGA sample and the as-deposited sample are 160 and 133 cm<sup>2</sup>/V s, respectively. Figure 3 compares the output characteristics. The current increases significantly after FGA.

We measured the total resistance of our device from the output curve at different channel lengths. The total resistance can be considered to be a contribution of the channel resistance and contact

**Figure 1.** (Color online) (a) Schematic representation of the cross-sectional view of the top-gate device structure. (b) Optical image of the flexible device at the bending stage and (c) transfer characteristics of the enhancement type of n-transistor in the as-deposited condition.

Figure 2. (Color online) Comparison of the (a) transfer characteristics between asdeposited, FGA, and HPHA device (inset in log scale) and (b) the corresponding transconductance curve between the asdeposited and the FGA sample.

**Figure 3.** (Color online) Output characteristics of the (a) as-deposited sample and after (b) FGA. The figure inset shows the total resistance of the devices before and after FGA.

Table I. Comparison of electrical properties between devices before and after FGA.

| Sample condition | On/off<br>ratio | $g_{ m m,max} \ (\mu { m S})$ | Mobility<br>(cm <sup>2</sup> /V s) | $V_{ m th}$ (V) | Subthreshold<br>slope<br>(V/dec) |

|------------------|-----------------|-------------------------------|------------------------------------|-----------------|----------------------------------|

| As-deposited     | $> 10^{6}$      | 8                             | 133                                | 10.8            | 0.7                              |

| FGA              | $> 10^{7}$      | 20                            | 160                                | 2.20            | 0.36                             |

| HPHA             | $> 10^{7}$      | 18                            | 155                                | 0.5             | 0.4                              |

resistance. We can separate the contact resistance by plotting the total resistance at different channel lengths (inset of Fig. 3a). From the figure we can conclude that the contact resistance of the device was improved by FGA but it cannot be responsible for the large  $V_{\rm th}$  shift alone. Further improvement can be caused by the defect passivation in both the interface and bulk sites after H<sub>2</sub> annealing even though the annealing temperature is quite low compared to that of the conventional method.

Table I summarizes all the electrical properties that have been

discussed so far. The mobility values presented here are quite low compared to  $SiO_2$  but are comparable to the reported  $Al_2O_3$  transistor on conventional complementary metal oxide semiconductor technology.<sup>20,21</sup>

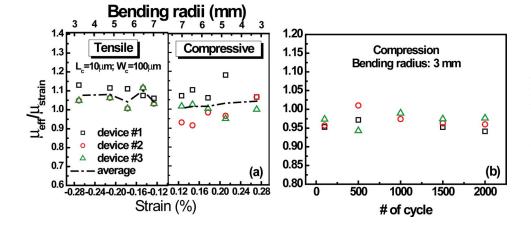

Next, the flexibility of the device was tested at different bending radii ( $R_c$ ). The ratio of the device mobility before and after bending against the bending radius and the corresponding strain values is plotted in Fig. 4a for each of the three devices and their averages. Very little degradation of mobility has been observed at  $R_c$  = 0.271 mm corresponding to <0.3% strain. Figure 4b shows the fatigue test after several cycles of bending at a bending radius of 3 mm (compressive stress).

In conclusion, a flexible transistor device with excellent flexibility has been demonstrated to have high mobility and low threshold voltage. Low off current, high on–off ratio, and high mobility have been achieved. The exact mechanism for improved device performance after annealing requires a much more detailed study, but better contact resistance and dielectric quality are responsible for better device properties. Additional  $H_2$  annealing is very promising for future flexible device application.

Figure 4. (Color online) (a) The mobility change in the devices at different bending radii (the smaller the radius, the larger the strain). (b) The normalized mobility after several cycles of bending. Both cases of mobility show very little change.

## Acknowledgments

This was supported by the IT R&D Program of the Ministry of Knowledge Economy of Korea (MKE 2008-F024-01, Development of Mobile Flexible IOP Platform).

Electronics and Telecommunications Research Institute assisted in meeting the publication costs of this article.

## References

- 1. J. Jang, Mater. Today, 9, 46 (2006).

- R. Reuss, B. Chalamala, A. Moussessian, M. Kane, A. Kumar, D. Zhang, J. Rogers, M. Hatalis, D. Temple, G. Moddel, et al., *Proc. IEEE*, 93, 1239 (2005).

- A. Facchetti, *Mater. Today*, **10**, 28 (2007).

D. Hines, A. Southard, and M. Fuhrer, *J. Appl. Phys.*, **104**, 024510 (2008).

- 5. K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Nature (London), 432, 488 (2004).

- W. Jackson, R. Hoffman, and G. Herman, *Appl. Phys. Lett.*, **87**, 193503 (2005).

C. Yang, L. Smith, C. Arthur, and G. Parsons, *J. Vac. Sci. Technol. B*, **18**, 683 (2000).

- 8. P. Carey, P. Smith, S. Theiss, and P. Wickboldt, J. Vac. Sci. Technol. A, 17, 1946 (1999)

- 9. M. Mietl, Z.-T. Zhu, V. Kumar, K. Lee, X. Feng, Y. Huang, I. Adesida, R. Nuzzo,

and J. Rogers, Nature Mater., 5, 33 (2006).

- 10. E. Menard, R. Nuzzo, and J. Rogers, Appl. Phys. Lett., 86, 093507 (2005).

- 11. J.-H. Ahn, H.-S. Kim, K. Lee, S. Jeon, S. Kang, Y. Sun, R. Nuzzo, and J. Rogers, Science, 314, 1754 (2006).

- 12. K. Gao, F. Speck, K. Emtsev, Th. Seyller, L. Ley, M. Oswald, and W. Hansch, Phys. Status Solidi A, 203, 2194 (2006).

- 13. A. Stesmans and V. Afanase'v, J. Vac. Sci. Technol. B, 20, 1720 (2002).

- 14. A. Kamgar, D. Monroe, and W. Mansfield, IEEE Electron Device Lett., 24, 448 (2003).

- 15. C.-H. Chung, Y.-H. Kim, J. Moon, M.-H. Lee, J. Lim, S. Yun, D.-J. Park, D.-W. Kim, and J. Lee, Appl. Phys. Lett., 88, 073516 (2006).

- 16. R. J. Carter, E. Cartier, A. Kerber, L. Pantisano, T. Schram, S. De Gendt, and M.

- Heyns, Appl. Phys. Lett., 83, 533 (2003).

17. M. Hasan, M. Jo, M. S. Rahman, H. Cho, S. Heo, and H. Hwang, Electrochem. Solid-State Lett., 9, F77 (2006).

- 18. Y. Son, M. Chang, H. Park, M. S. Rahman, S. Baek, and H. Hwang, Electrochem. Solid-State Lett., 10, H324 (2007). 19. Z.-T. Zhu, E. Menard, K. Hurley, R. Nuzzo, and J. Rogers, Appl. Phys. Lett., 86,

- 133507 (2005).

- 20. S. Guha, E. Gusev, H. Okorn-Schidt, M. Copel, L.-A. Ragnarsson, and N. Bojarczuk, Appl. Phys. Lett., 81, 2956 (2002).

- 21. K. Torii, Y. Shimamoto, S. Saito, K. Obata, T. Yamauchi, D. Hisamoto, T. Onai, and M. Hiratani, Microelectron. Eng., 65, 447 (2003).