## Impact of Sn/Zn ratio on the gate bias and temperature-induced instability of Zn-In-Sn-O thin film transistors

Cite as: Appl. Phys. Lett. **95**, 173508 (2009); https://doi.org/10.1063/1.3257726 Submitted: 15 August 2009 . Accepted: 10 October 2009 . Published Online: 29 October 2009

Min Ki Ryu, Shinhyuk Yang, Sang-Hee Ko Park, Chi-Sun Hwang, and Jae Kyeong Jeong

## ARTICLES YOU MAY BE INTERESTED IN

High performance thin film transistor with cosputtered amorphous Zn-In-Sn-O channel: Combinatorial approach

Applied Physics Letters 95, 072104 (2009); https://doi.org/10.1063/1.3206948

Origin of threshold voltage instability in indium-gallium-zinc oxide thin film transistors Applied Physics Letters **93**, 123508 (2008); https://doi.org/10.1063/1.2990657

High-mobility thin-film transistor with amorphous InGaZnO<sub>4</sub> channel fabricated by room temperature rf-magnetron sputtering Applied Physics Letters **89**, 112123 (2006); https://doi.org/10.1063/1.2353811

Appl. Phys. Lett. **95**, 173508 (2009); https://doi.org/10.1063/1.3257726 © 2009 American Institute of Physics.

## Impact of Sn/Zn ratio on the gate bias and temperature-induced instability of Zn-In-Sn-O thin film transistors

Min Ki Ryu,<sup>1</sup> Shinhyuk Yang,<sup>1</sup> Sang-Hee Ko Park,<sup>1</sup> Chi-Sun Hwang,<sup>1</sup> and Jae Kyeong Jeong<sup>2,a)</sup>

<sup>1</sup>Transparent Electronics Team, ETRI, Daejeon 305-700, Republic of Korea

<sup>2</sup>Department of Materials Science and Engineering, Inha University, 253 Yonghyun-Dong, Nam-Gu, Incheon 402-751, Republic of Korea

(Received 15 August 2009; accepted 10 October 2009; published online 29 October 2009)

We investigated the effect of the Sn/Zn ratio in the amorphous Zn-In-Sn-O (ZITO) system on the gate voltage stress-induced stability of the resulting thin film transistors (TFTs). The device stability of the TFTs with a composition channel of Zn:In:Sn=0.35:0.20:0.45 (device C) was dramatically improved, while those of the devices with Zn:In:Sn=0.45:0.20:0.35 and 0.40:0.20:0.40 suffered from deep level trap creation in the channel and charge trapping, respectively. The stability enhancement of device C can be attributed to its having the lowest total trap density, which was corroborated by the superior temperature stability of the subthreshold current region in the temperature range from 298 to 398 K. Therefore, the Sn atoms are believed to act as a stabilizer of the amorphous ZITO network, which is similar to the role of Ga in the In-Ga-Zn-O system. © 2009 American Institute of Physics. [doi:10.1063/1.3257726]

Zn-based oxide semiconductors have attracted a tremendous amount of attention as the active channel material of emerging electronic devices including the thin film transistors (TFTs) backplanes for flexible displays or transparent active matrix organic light-emitting diode displays, because they offer high performance parameters, such as a high mobility, low gate subthreshold swing, and excellent uniformity as well as the advantages of good transparency to visible light and low temperature process capability compared with amorphous Si and polycrystalline Si TFTs.<sup>1–6</sup>

However, the instability of the threshold voltage  $(V_{th})$  of Zn-based oxide TFTs under gate voltage stress is one of the most crucial problems remaining to be resolved before oxide TFTs can be integrated into commercial electronic products. Several groups attributed the positive V<sub>th</sub> shift under positive gate voltage stress (PGVS) for oxide TFTs to charge trapping at or near the Zn-based oxide channel and gate dielectric, based on the amorphous silicon framework.<sup>7–10</sup> It should be noted, however, that almost all of the devices that were studied were bottom gate oxide TFTs in which the channel layer was directly exposed to the ambient atmosphere (i.e., unpassivated devices). Because the electrical properties of ZnO and SnO<sub>2</sub> semiconductors are extremely affected by the presence of an ambient atmosphere (oxygen, water, and hydrogen), the interaction between these channel layer and ambient molecules cannot be neglected during the stability evaluation of oxide TFTs.<sup>11-14</sup> Indeed, one of the authors recently asserted that the Vtth instability of oxide TFTs under gate voltage stress comes from the gate-field-induced molecular adsorption/desorption of oxygen, hydrogen, or water on the back channel surface, rather than the aforementioned charge trapping phenomena.<sup>15</sup> This complexity of the oxide TFT system have prevented unambiguous and in-depth studies from being conducted to determine the exact relationship between the channel material properties (channel composition, and film density) and the resulting transistor instability.

In this letter, we chose the bottom gate and bottom contact device configuration, in which a 20-nm-thick Al<sub>2</sub>O<sub>3</sub> protection layer and 20-nm-thick Al<sub>2</sub>O<sub>3</sub> passivation layer deposited by atomic layer deposition (ALD) were formed on the Zn-In-Sn-O (ZITO) semiconductor film. Al<sub>2</sub>O<sub>3</sub> thin film was used as a passivation layer, because ALD-derived Al<sub>2</sub>O<sub>3</sub> layers are known to act as an efficient diffusion barrier against the penetration of oxygen or water.<sup>16-18</sup> Therefore, the gate voltage stress-dependent device instabilities can be attributed to the charge trapping or the channel degradation rather than the ambient-related deterioration, which renders the interpretation of the device instability mechanism more obvious. It was found that the Sn/Zn ratio greatly affected not only the device performance but also the dc and temperature instability of the ZITO transistors. The extremely low trap density of the devices, including the interfacial trap density and semiconductor bulk trap density is closely related to their excellent dc and temperature stability.

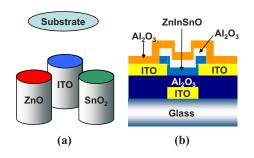

Lithographically patterned ITO (150nm) on an alkali free-glass (E2000, Samsung Corning Inc.) substrate with a surface area of  $100 \times 100 \text{ mm}^2$  was used as the gate electrode for the bottom gate TFT.  $Al_2O_3$  (185nm) film as a gate dielectric was deposited by ALD at 150 °C. The ITO electrode used as a source/drain electrode was deposited by the conventional sputtering method and then patterned using photolithography and wet etching. The a-ZITO film with a thickness of 25nm was grown by the cosputtering of ZnO, SnO<sub>2</sub>, and ITO (In<sub>2</sub>O<sub>3</sub>, 90 wt %) targets. A schematic diagram of the target-substrate arrangement in the cosputtering system is shown in Fig. 1(a). Then, the 20-nm-thick Al<sub>2</sub>O<sub>3</sub> film as a protection layer was deposited by plasma enhanced ALD at 150 °C. After patterning the active channel and protection layer using photolithograph and subsequent wet etching, a second  $Al_2O_3$  (20 nm) film was formed as a passivation layer by ALD at 150 °C. Finally, the fabricated devices were subjected to thermal annealing at 300 °C for 2 hrs under an O2 atmosphere. A schematic cross-section of the fab-

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: jkjeong@inha.ac.kr.

FIG. 1. (Color online) (a) Schematic diagram of the target-substrate arrangement in the cosputtering system. (b) Schematic cross-section of the fabricated ZITO TFTs with a bottom gate and bottom contact structure (W/L=40/20  $\mu$ m).

ricated ZITO TFTs is depicted in Fig. 1(b). The IV characteristics of the ZITO devices were measured at various temperatures ranging from 298 to 398 K with an Agilent 4156C precision semiconductor parameter analyzer.

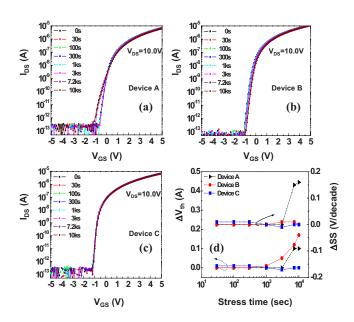

In the ternary system of  $ZnO-In_2O_3-SnO_2$ , the  $In_2O_3$ fraction is the most significant component determining the field-effect mobility. However, a higher In content results in the deterioration of the threshold voltage.<sup>19</sup> Thus, the indium composition was fixed at an atomic ratio of In/(Zn+In +Sn) of 0.20. Sn and Zn compositions of 0.35 and 0.45 (device A), 0.40 and 0.40 (device B), and 0.45 and 0.35 (device C) were employed, respectively. The field-effect mobilities ( $\mu_{FE}$ ) for devices A (24.1 cm<sup>2</sup>/V s) and B  $(24.6 \text{ cm}^2/\text{V s})$  were comparable to each other while the subthreshold gate swing (SS, 0.23 V/decade) of device B was better that (0.15 V/decade) of device A. On the other hand, device C exhibited a slightly reduced  $\mu_{\mathrm{FE}}$  $(15.1 \text{ cm}^2/\text{V s})$  and the best SS value of 0.11 V/decade. However, it should be noted that these device parameters correspond to the state-of-the-art characteristics for any Znbased oxide TFT. Figures 2(a)-2(c) show the evolution of the transfer curves as a function of the applied stress time for devices A, B, and C, respectively. The devices were stressed

FIG. 2. (Color online) The evolution of the transfer curves for devices (a) A, (b) B, and (c) C with a top gate and bottom contact structure (W/L =  $40/20 \ \mu$ m). (d) The variations in the  $\Delta V_{th}$  shift and  $\Delta$ SS value for devices A, B, and C.

under the following conditions: the  $V_{GS}$  was set to 10.0 V and V<sub>DS</sub> was fixed at 0 V. The maximum stress duration was 10 000 sec. It can be seen that while device A shows a significant deterioration in its S value as well as a positive V<sub>th</sub> shift ( $\sim 0.1$  V) with increasing stress time, device B did not suffer from any change of the S value and exhibited only a parallel positive  $V_{th}$  shift as shown in Fig. 2(d). The increase  $(\Delta SS=0.16 \text{ V/decade})$  in the subthreshold swing for device A after a PGVS of 10<sup>4</sup> sec can be attributed to the creation of deep-level defects ( $\sim 6.3 \times 10^{11}$ /cm<sup>2</sup>) in the ZITO channel layer during the application of the gate voltage stress.<sup>20</sup> In contrast, device B exhibited typical behavior i.e., a positive  $V_{th}$  shift (~0.17 V) after a the PVGS of 10<sup>4</sup> sec, indicating that charge trapping occurred at the interface between the ZITO channel and Al<sub>2</sub>O<sub>3</sub> gate dielectric. It is noted that the fast recovery of the V<sub>th</sub> value occurred without any thermal annealing after one day indicating that the activation energy for detrapping at the charge trapping site injection is comparable to or less than the thermal energy (approximately 0.025 eV) at room temperature. Thus, we excluded the possibility of charge injection into the Al<sub>2</sub>O<sub>3</sub> dielectric layer. Finally, device C showed excellent stability against the gate voltage stress. There was no degradation of the  $\mu_{\rm FE}$  and SS values, nor any shift in the Vtth value during application of the PGVS for 10<sup>4</sup> sec. The absence of charge trapping after the PGVS might be related to the fact that the interfacial traps density (Nit) of device C is lower than those of devices A and B. The maximum N<sub>it</sub> value can be estimated from the SS value  $[N_{it}=[SS \log(e)/(kT/q)-1]C_i/q,^{19}$  where  $C_i$  is the gate capacitance per unit area, k is the Boltzmann constant, T is the absolute temperature, and q is the elementary electron charge], which assumes that there is no semiconductor bulk trap  $(N_{ss})$  in the ZITO thin film. The  $N_{it,max}$  value (2.1  $\times 10^{11}$ /cm<sup>2</sup>) for device C was much smaller than those  $(7.8 \times 10^{11}/\text{cm}^2, 6.7 \times 10^{11}/\text{cm}^2)$  for devices A and B. This lower N<sub>it</sub> might constitute the reason why no V<sub>th</sub> shift caused by charge trapping was observed for device C. Now it is obvious that the ratio of Sn/Zn is critical to the effect of charge trapping and/or trap creation including N<sub>ss</sub> and D<sub>it</sub> after the PGVS. The absence of any shift in V<sub>th</sub> under PGVS for devices C would suggest the ruling out of charge injection into the  $Al_2O_3$  gate dielectric layer as the origin of the positive V<sub>th</sub> shift of device B. It should be noted that the V<sub>th</sub> shift for the unpassivated device with the same channel composition of device C was more than 1.0V under the identical PGVS condition (data not shown), indicating that the passivation is indeed crucial to prevent the effect of ambient effect. Furthermore, the fact that increasing the Sn content from 35% to 45% significantly improved the dc stability of the resulting ZITO transistors with the bottom gate structure suggests that the role of the Sn ion may be that of a stabilizer of the amorphous ZITO network and an annihilator of the overall trap sites including N<sub>it</sub> and N<sub>ss</sub>.

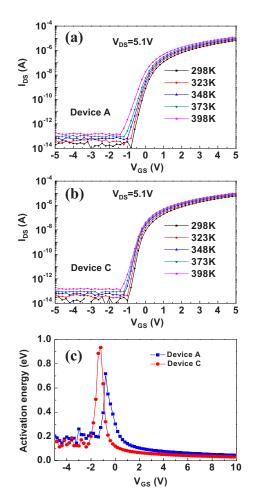

Figures 3(a) and 3(b) show the evolution of the transfer curves as a function of the measurement temperature for devices A and C, respectively. It can be seen that  $V_{th}$  is negatively shifted with increasing temperature for both devices. Though the  $V_{th}$  value for device A was shifted by approximately 0.4 V from 0.2 to -0.2 V, the negative  $V_{th}$  shift in device C after increasing the measurement temperature from 298 to 398 K was relatively small (~0.2 V). This negative  $V_{th}$  shift with increasing temperature can be explained by the

FIG. 3. (Color online) The evolution of the transfer curves as a function of the measurement temperature for devices (a) A and (b) C. (c) Variations of the activation energy ( $E_A$ ) of the  $I_{DS}$  vs  $V_{GS}$  for devices A and C.

thermal activation process of the subthreshold drain current. The conductance activation energy  $(E_A)$  can be calculated as a function of  $V_{GS}$  in the forbidden bandgap from the fitting of the temperature-dependent  $log(I_{DS})$  versus 1/T curve, where  $E_A = E_C - E_F$  assuming Boltzmann statistics.<sup>21,22</sup> Figure 3(c) shows  $E_A(=E_C-E_F)$  as a function of  $V_{GS}$  for devices A and C. The maximum E<sub>A</sub> value (0.72 eV) for devices A was observed at a  $V_{GS}$  of -0.8 V and gradually decreased to 0.2 eV at a V<sub>GS</sub> of 0.4 V. In contrast, the highest energy barrier for device C was approximately 0.93 eV at a  $V_{GS}$  of -1.2 V and  $E_{\rm A}$  rapidly decreased to 0.2 eV at a  $V_{GS}$  of -0.6 V. The falling rate of EA with respect to VGS in the subthreshold current region should have the same magnitude as the rising rate of E<sub>F</sub>. In the case of a TFT having a significantly large trap density  $(N_{total})$  including  $N_{SS}$  and  $N_{it}$ , the rate of change of  $E_F$  with respect to  $V_{GS}$  ( $\partial E_F / \partial V_{GS}$ ) is roughly inversely proportional to the magnitude of N<sub>total</sub>, because all of trap sites below  $E_F$  must be fulfilled with electron before a move to the E<sub>F</sub> level in the forbidden bandgap region become possible. Thus, the much faster falling rate  $(|\Delta E_F / \Delta V_{GS}| \sim 1.2 \text{ eV} / \text{V})$  of  $E_A$  in device C compared to that  $(|\Delta E_F / \Delta V_{GS}| \sim 0.43 \text{ eV} / \text{V})$  of device A, means that the N<sub>total</sub> value is reduced by approximately 3 times compared to that of device A. This speculation is quite consistent with the aforementioned N<sub>it.max</sub> values, which were calculated from the SS values. Therefore, the better temperature stability as well as dc stability for device C can be attributed to the much reduced  $N_{total}$  at the channel/gate dielectric interface and ZITO bulk film.

In summary, the effect of the Sn/Zn ratio in amorphous ZITO semiconductors on the device stability of the resulting TFTs was investigated. With increasing Sn/Zn ratio from 0.35/0.45 to 0.45/0.35, the  $\mu_{\rm FE}$  and SS values of the ZITO TFT were slightly decreased and dramatically improved, respectively. The dc stability was highly dependent on the cation composition: the optimized Sn/Zn ratio of 0.45/0.35 resulted in the excellent temperature stability as well as dc stability of the ZITO TFTs. Therefore, it was concluded that the ZITO semiconductor system can be a promising candidate for TFTs with excellent stability as well as high performance, thereby replacing the commercially available amorphous Si and polycrystalline Si TFTs.

This work was supported by the IT R&D program of the Ministry of Knowledge Economy (Grant No. 2006-S079-04, smart window with transparent electronic devices). J.K.J. ac-knowledges the support from Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology (Grant No. 2009-0087297).

- <sup>1</sup>K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirono, and H. Hosono, Nature (London) **432**, 488 (2004).

- <sup>2</sup>E. M. C. Fortunato, P. M. C. Barquinha, A. C. M. B. G. Pimentel, A. M. F. Goncalves, A. J. S. Marques, L. M. N. Pereira, and R. F. P. Martins, Adv. Mater. **17**, 590 (2005).

- <sup>3</sup>H. Q. Chiang, J. F. Wager, and R. L. Hoffman, Appl. Phys. Lett. **86**, 013503 (2005).

- <sup>4</sup>H. Yabuta, M. Sano, K. Abe, T. Aiba, T. Den, H. Kumomi, K. Nomura, T. Kamiya, and H. Hosono, Appl. Phys. Lett. **89**, 112123 (2006).

- <sup>5</sup>J. K. Jeong, H.-J. Chung, Y.-G. Mo, and H. D. Kim, J. Electrochem. Soc. **155**, H873 (2008).

- <sup>6</sup>J. H. Jeong, H. W. Yang, J.-S. Park, J. K. Jeong, Y.-G. Mo, H. D. Kim, J.

- Song, and C. S. Hwang, Electrochem. Solid-State Lett. 11, H157 (2008).

- <sup>7</sup>R. B. M. Cross and M. M. De Souza, Appl. Phys. Lett. **89**, 263513 (2006).

- <sup>8</sup>P. Gorrn, P. Holzer, T. Riedl, W. Kowalsky, J. Wang, T. Weimann, P. Hinze, and S. Kipp, Appl. Phys. Lett. **90**, 063502 (2007).

- <sup>9</sup>Y. Vygranenko, K. Wang, and A. Nathan, Appl. Phys. Lett. **91**, 263508 (2007).

- <sup>10</sup>A. Suresh and J. F. Muth, Appl. Phys. Lett. **92**, 033502 (2008).

- <sup>11</sup>D. Kang, H. Lim, C. Kim, I. Song, J. Park, Y. Park, and J. G. Chung, Appl. Phys. Lett. **90**, 192101 (2007).

- <sup>12</sup>J.-S. Park, J. K. Jeong, H.-J. Chung, Y.-G. Mo, and H. D. Kim, Appl. Phys. Lett. **92**, 072104 (2008).

- <sup>13</sup>Q. H. Li, Q. Wan, Y. X. Liang, and T. H. Wang, Appl. Phys. Lett. 84, 4556 (2004).

- <sup>14</sup>D. Zhang, C. Li, S. Han, X. Liu, T. Tang, W. Jin, and C. Zhou, Appl. Phys. Lett. 82, 112 (2003).

- <sup>15</sup>J. K. Jeong, H. W. Yang, J. H. Jeong, Y.-G. Mo, and H. D. Kim, Appl. Phys. Lett. **93**, 123508 (2008).

- <sup>16</sup>H. Jeon, K. Shin, C. Yang, C. E. Park, and S.-H. Ko Park, Appl. Phys. Lett. **93**, 163304 (2008).

- <sup>17</sup>S.-H. Ko Park, J. Oh, C.-S. Hwang, J.-I. Lee, Y. S. Yang, and H. Y. Chu, Electrochem. Solid-State Lett. 8, H21 (2005).

- <sup>18</sup>D. H. Levy, D. Freeman, S. F. Nelson, P. J. Cowdery-Corvan, and L. M. Irving, Appl. Phys. Lett. **92**, 192101 (2008).

- <sup>19</sup>M. K. Ryu, S. Yang, S.-H. Ko Park, C.-S. Hwang, and J. K. Jeong, Appl. Phys. Lett. **95**, 072104 (2009).

- <sup>20</sup>J. Kanicki and S. Martin, in *Thin-Film Transistor*, edited by C. Kagan and P. Andry (Marcel Dekker, New York, 2003), p. 87.

- <sup>21</sup>H. C. Slade, M. S. Shur, S. C. Deane, and M. Hack, Appl. Phys. Lett. **69**, 2560 (1996).

- <sup>22</sup>L. Pichon, A. Mercha, R. Carin, O. Bonnaud, T. Mohammed-Brahim, Y. Helen, and R. Rogel, Appl. Phys. Lett. **77**, 576 (2000).