## INVITED PAPER Special Section on Electronic Displays

# **Al-Zn-Sn-O** Thin Film Transistors with Top and Bottom Gate Structure for AMOLED

Doo-Hee CHO<sup>†a)</sup>, Sang-Hee Ko PARK<sup>†</sup>, Shinhyuk YANG<sup>†</sup>, Chunwon BYUN<sup>†</sup>, Min Ki RYU<sup>†</sup>, Jeong-Ik LEE<sup>†</sup>, Chi-Sun HWANG<sup>†</sup>, Sung Min YOON<sup>†</sup>, Hye Yong CHU<sup>†</sup>, *and* Kyoung Ik CHO<sup>†</sup>, *Nonmembers*

**SUMMARY** We have fabricated the transparent bottom gate and top gate TFTs using new oxide material of Al-Zn-Sn-O (AZTO) as an active layer. The AZTO active layer was deposited by RF magnetron sputtering at room temperature. Our novel TFT showed good TFT performance without post-annealing. The field effect mobility and the sub-threshold swing were improved by the post-annealing, and the mobility increased with SnO<sub>2</sub> content. The AZTO TFT (about 4 mol% AlOx, 66 mol% ZnO, and 30 mol% SnO<sub>2</sub>) exhibited a mobility of 10.3 cm<sup>2</sup>/Vs, a turn-on voltage of 0.4 V, a sub-threshold swing of 0.6 V/dec, and an on/off ratio of 10<sup>9</sup>. Though the bottom gate AZTO TFT showed good electrical performance, the bias stability was relatively poor. The bias stability was significantly improved in the top gate AZTO TFT. We have successfully fabricated the transparent AMOLED panel using the back-plane composed with top gate AZTO TFT array.

key words: thin film transistor, oxide, AMOLED, transparent

## 1. Introduction

New flat panel displays based on organic light emitting diodes (OLED) have attracted interests because they are considered as blue ocean electronic products. Small-size active matrix OLED (AMOLED) displays are already used on mobile phones. The reliable TFT back-plane showing good electrical performance is indispensable for large-size AMOLED and it should be manufactured at low temperature for the flexible displays which are commercially available. In recent time, the flat panel display televisions demand high resolution, large size, fast response, and low power consumption. As the display size and resolution increases, the TFT back-plane with good uniformity and high stability is required [1]. Conventional a-Si TFT can be fabricated with high uniformity and low cost, however its mobility and bias stability are poor. LTPS (low temperature poly silicon) TFT has disadvantages for large size production due to relatively poor uniformity and high cost [2]. For these reasons, oxide TFT back-planes are considered as prominent candidate for the driving device of AMOLED. There are some candidates for oxide TFT material, and the oxide TFTs using ZnO [3], In-Zn-O [4], Zn-Sn-O [5], IGZO [6]-[8], and Al-Zn-Sn-O [9] as active channel material have been widely studied. Zn-Sn-O TFT is generally required high temperature (> 300°C) processing to represent a good electrical performance [5]. Several studies concerning about the oxide TFTs processed at low temperature (<  $150^{\circ}$ C) were reported, however the electrical performances were relatively poor [10]. We have successfully fabricated the oxide TFTs with a novel active layer which was composed with Al<sub>2</sub>O<sub>3</sub>-ZnO-SnO<sub>2</sub> (AZTO) and sputtered at room temperature [9], [11]. Al<sup>3+</sup> is not a heavy-metal cation, therefore, the addition of  $Al_2O_3$  is considered not to enhance the electron transport. However, addition of Al<sup>3+</sup> may enhance the chemical and electrical stability like Ga<sup>3+</sup> in In-Ga-Zn-O system [12]. The AZTO material is very stable chemically, and sputtering method has advantages on low cost and large area uniformity among various deposition methods. Therefore, the AZTO TFT is prominent device for driving the large size AMOLED panel. In this paper, we report the electrical characteristics and gate bias stabilities depending on TFT structures.

#### 2. Experimental Procedure

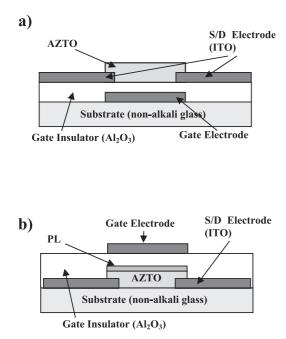

We have fabricated bottom gate and top gate TFTs with the new active material sputtered at room temperature. The novel active material was composed with amorphous oxide of Al<sub>2</sub>O<sub>3</sub>-ZnO-SnO<sub>2</sub>. The schematic diagram of the AZTO TFT with the bottom gate and the top gate structure are shown in Fig. 1. The TFTs have a co-planar structure in the bottom gate structure and a staggered structure in the top gate structure. A  $100 \times 100 \text{ mm}^2$  alkaline-free glass was used as a substrate after the ultrasonic cleaning with acetone, iso-propyl alcohol and DI water in sequence. Gate and source/drain electrodes were constituted with 150 nm thick indium tin oxide (ITO). A gate insulator of Al<sub>2</sub>O<sub>3</sub> was formed by atomic layer deposition (ALD) method at 150° and its thickness was 185 nm. An aluminum precursor was tri-methyl aluminum and an oxygen precursor was water vapor. An active layer of AZTO was formed by co-sputtering of an Al<sub>2</sub>O<sub>3</sub>-ZnO target and a SnO<sub>2</sub> target with an off-axis type RF magnetron sputter at room temperature. The sputtering was performed in the atmosphere of Ar and O<sub>2</sub> mixed gas with the chamber pressure of 0.2 Pa. All patterning processes were performed by conventional photo-lithographic method and wet etching process. The post-annealing was performed in vacuum using electric ovens. The electrical characteristics of the TFTs were measured with a semiconductor parameter analyzer (Agilent B1500A). The bias stabilities of the TFTs were measured with other semiconductor analyzer (HP 4145B). All the electrical measurements

Manuscript received March 2, 2009.

Manuscript revised May 15, 2009.

<sup>&</sup>lt;sup>†</sup>The authors are with ETRI, Daejon, 305-700, Korea.

a) E-mail: chodh@etri.re.kr

DOI: 10.1587/transele.E92.C.1340

Fig. 1 The structure of the a) bottom gate and b) top gate AZTO TFT.

were carried out in air at room temperature. The bias stability measurements were performed under stress condition of  $V_g = +20$  V and  $V_{ds} = 0$  V. X-ray diffraction (XRD) spectra of the AZTO films were recorded with a Rigaku RU-200BH diffractometer using CuK $\alpha$  radiation. The chemical composition of the AZTO thin film was analyzed by Auger electron spectroscopy (AES) method. The electrical properties including the field effect mobility ( $\mu_{FET}$ ), the turn-on voltage ( $V_{on}$ ), the on-off current ratio ( $I_{on}/I_{off}$ ) and the sub-threshold swing (S/S) were calculated from the data of the transfer curve under 15.5 V source-drain voltage.

#### 3. Results and Discussion

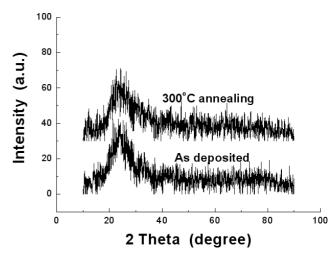

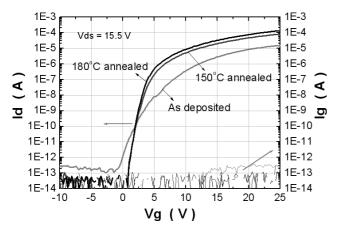

The thin films of AZTO deposited by RF magnetron sputtering were amorphous. Figure 2 shows the XRD spectra of AZTO thin films deposited on Si wafer by RF magnetron sputtering before and after annealing. There was no diffraction peak of crystalline phase in the XRD spectra even after the 300°C annealing. The AZTO active layer of the TFT was considered as very stable amorphous oxide material. Amorphous oxide active layer has advantages on large area uniformity and long-term reliability because it has no grain boundary [12]. Figure 3 shows the transfer characteristics of the bottom gate AZTO TFTs (W/L =  $40 \,\mu m/20 \,\mu m$ ) without heat treatment and after 150°C and 180°C annealing in vacuum. The composition of the active layer measured by AES was about 4 mol% AlOx, 66 mol% ZnO, and 30 mol% SnO<sub>2</sub>. The AZTO TFT prepared at room temperature showed the  $\mu_{\text{FET}}$  of 1.9 cm<sup>2</sup>/Vs, the  $V_{\text{on}}$  of near -2.0 V, the  $I_{on}/I_{off}$  of more than 10<sup>7</sup>. The off-current level was under  $10^{-12}$  A and the S/S was relatively large. The  $150^{\circ}$ C annealed TFT exhibited the  $\mu_{\text{FET}}$  of  $6.2 \,\text{cm}^2/\text{Vs}$ , the  $V_{\text{on}}$  of 0.9 V, the  $I_{on}/I_{off}$  of about 10<sup>9</sup> and the S/S of 0.60 V/dec.

Fig. 2 XRD spectra of AZTO thin films before and after annealing.

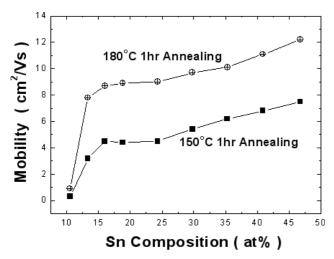

The 180°C annealed TFT exhibited the  $\mu_{\text{FET}}$  of 10.1 cm<sup>2</sup>/Vs, the  $V_{\rm on}$  of 0.9 V, the  $I_{\rm on}/I_{\rm off}$  of more than 10<sup>9</sup> and the S/S of 0.58 V/dec. It can be seen that the mobility increased with increasing the annealing temperature. The sub-threshold swing and the on-off current ratio were also improved with increasing annealing temperature. The turn-on voltage of the AZTO TFT was -1.1 V before the annealing. The turnon voltage shifted to near 0 V by the low temperature annealing. Electrical performance was sufficiently good for the application to active matrix displays just by post-annealing at the temperature higher than 150°C. The electrical properties improved by post annealing up to about 250°C, and scarcely improved above 250°C. The electron transport properties of the as-deposited films fabricated at the inadequate condition are known to be improved by thermal annealing to a level which is almost the same as that in the films deposited at the optimized condition [13]. The AZTO active layer deposited by room temperature sputtering was supposed not to be optimized and improved by the post annealing. The field effect mobility changes with SnO2 composition are shown in Fig.4. The mobilities in Fig.4 were measured for the bottom gate AZTO TFTs with the active layer composition of  $xSn(1-x)(Al_{0.06}Zn_{0.94})O_y$ . The mobility increased with SnO<sub>2</sub> content, and the mobility change was large until 16 mol% of SnO<sub>2</sub>, from then, the mobility increment became slowdown. Below 10 mol% of SnO<sub>2</sub>, the AZTO thin film did not show the field effect transistor characteristics, thus the mobility could not be measured. Amorphous oxides composed of heavy-metal cations with  $(n-1)d^{10} ns^0$   $(n \ge 4)$ electronic configurations show high electron mobilities because ns<sup>0</sup> ( $n \ge 4$ ) orbitals overlap between adjacent orbitals. The large diameter and spherical symmetry of the ns<sup>0</sup> orbitals lead high degree of overlap and conduction band dispersion [5], [12]. In the AZTO thin films,  $Sn^{4+}$  and  $Zn^{2+}$  are such heavy-metal cations. As a result of the mobility dependence on SnO<sub>2</sub> content in Fig. 4, Sn<sup>4+</sup> is supposed to control the field effect mobility rather than  $Zn^{2+}$  because  $5s^0$  orbital of  $\text{Sn}^{4+}$  is larger than  $4\text{s}^0$  orbital of  $\text{Zn}^{2+}$  [12].

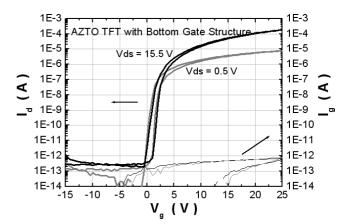

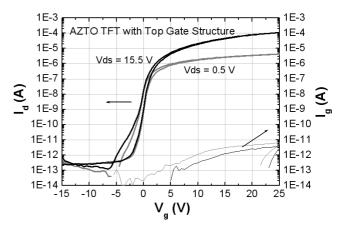

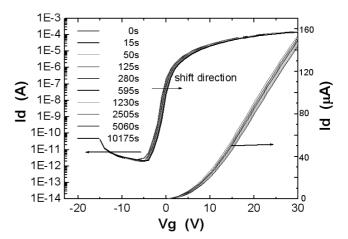

Figures 5 and 6 show the transfer characteristics of the

Fig. 3 Transfer characteristic change of AZTO TFTs with annealing temperature.

Fig. 4 The field effect mobility change with  $SnO_2$  content in AZTO active layer.

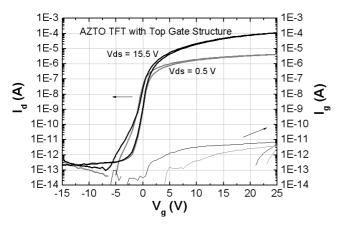

bottom gate and the top gate AZTO TFT after annealing at 250°C, respectively. The composition and sputtering condition of active layer, the gate insulator material and thickness were same in both cases. The turn-on voltage of the top gate AZTO TFT was about -5 V, while that of the bottom gate TFT was near 0 V. The  $\mu_{\text{FET}}$ 's of the bottom gate TFT and the top gate TFT were  $10.3 \text{ cm}^2/\text{Vs}$  and  $6.0 \text{ cm}^2/\text{Vs}$ , respectively. The top gate TFT showed shoulders in the sub-threshold region as shown in Fig. 6. In the bottom gate structure the interface between active layer and gate insulator is damaged by ITO and active layer sputtering process. Since those sputtering damages were partially recovered by post-annealing, the electrical properties were improved by the post-annealing. On the other hand, the active layer and the interface of the top gate structure may be contaminated or damaged during the active layer patterning and gate insulator deposition process. We have patterned the active layer by conventional photo-lithography method. Thus, the active layer surface might be contaminated by photoresist and PR stripper. The surface contamination is connected to the

**Fig. 5** Transfer characteristics of the bottom gate AZTO TFT after annealing at 250°C.

Fig. 6 Transfer characteristics of the top gate AZTO TFT after annealing at  $250^{\circ}$ C.

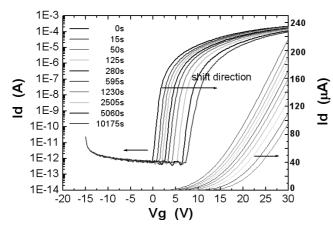

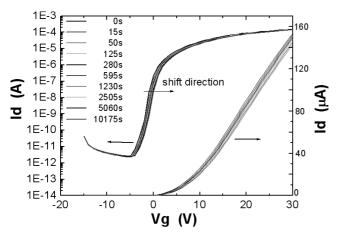

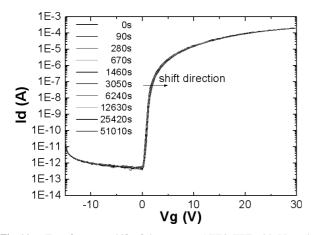

active-insulator interface defects. The Al2O3 gate insulator was deposited by atomic layer deposition (ALD) method using tri-methyl aluminum and water vapor at high temperature so that the active-insulator interface in the top gate TFT might be contaminated with hydrogen and carbon related defects. It is thought that such defects are hard to be eliminated sufficiently and may cause the sub-threshold region shoulders and the decrease of mobility. Those defects can be reduced by an appropriate gate insulator deposition process and post-annealing. Figures 7 and 8 show the gate bias stabilities of the bottom gate and the top gate AZTO TFT, The shift of  $V_{on}$  of the bottom gate AZTO respectively. TFT and the top gate AZTO TFT under +20 V of gate bias after 14 hrs was 7.6 V and 0.8 V, respectively. The gate bias stability of the top gate AZTO TFT was improved significantly compared to that of the bottom gate TFT. The gate bias instability is thought to originate primarily from charge trapping considering the direction of the  $V_{\rm on}$  shift. The interface between active layer and gate insulator of the bottom gate TFT may have a lot of electron traps compared to the top gate TFT. A large part of the insulator interface damage that causes the degradation of  $\mu_{\text{FET}}$  and S/S is supposed to be eliminated by post-annealing at a high temperature for

Fig. 7 Transfer curve shift of the bottom gate AZTO TFT annealed at  $250^{\circ}$ C under the +20 V gate bias voltage.

Fig. 8 Transfer curve shift of the top gate AZTO TFT annealed at  $250^{\circ}$ C under the +20 V gate bias voltage.

the bottom gate structure. However the charge traps degrading the bias stability can't be eliminated sufficiently in the bottom gate TFTs just by the post-annealing. In the case of the top gate structure, the electrical characteristics did not improved to a level of the bottom gate TFT by the postannealing, while the gate bias stability was significantly improved compared to that of the bottom gate TFT. The origins suffering the electrical characteristics are supposed to be different from those suffering the bias stability.

The top gate structure has advantages on the bias stability and is appropriate for the driving devices of AMOLED. We investigated the optimum process for the AZTO TFT with top gate structure. The control of the active-insulator interface was thought to be the most important process for controlling final electrical characteristics of the top gate TFT. Before the active layer patterning and the gate insulator deposition, we deposited the thin (30 nm) Al<sub>2</sub>O<sub>3</sub> protective layer (PL) on the active layer with plasma enhanced ALD in order to reduce the active-insulator interface contamination of hydrogen and carbon related defects. The oxygen precursor for ALD was not water vapor but oxygen plasma in the PL process. The PL was deposited after the active

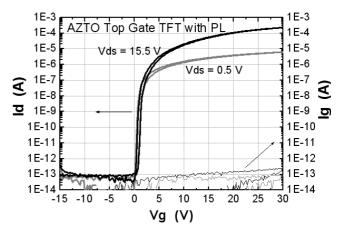

Fig.9 Transfer characteristics of the top gate AZTO TFT with PL after annealing at  $300^{\circ}$ C.

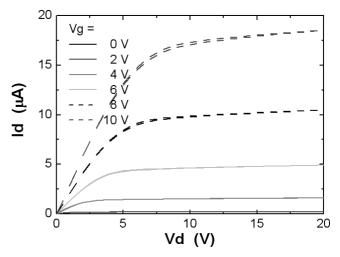

Fig. 10 Output characteristics of the top gate AZTO TFT with PL after annealing at  $300^{\circ}$ C.

layer deposition and active patterning was carried out after the PL deposition. Therefore, the contamination of the interface between active and insulator by photoresist and PR stripper was not occurred. Figures 9 and 10 show the transfer and output characteristics of the AZTO TFT including the PL after annealing at 300°C, respectively. The shoulders in sub-threshold region were almost disappeared and the *S*/*S* was significantly improved to 0.15 V/dec. The  $\mu_{\text{FET}}$ of the PL-included AZTO TFT with top gate structure increased up to 9.5 cm<sup>2</sup>/Vs. It was similar value to  $\mu_{\text{FET}}$  of the bottom gate TFT. Figure 11 shows the gate bias stability of the top gate AZTO TFT including the PL. The shift of  $V_{\text{on}}$ was smaller than 0.2 V after 14 hour gate bias stress.

In the case of the top gate TFT including the PL, the S/S and hysteresis were poor after annealing below 250°C. However, the 300°C annealing improved them remarkably. The PL and post-annealing at relatively high temperature was effective to improve not only the electrical characteristics but also the bias stability. For comparison, the transfer curve and gate bias stability characteristics of the 300°C an-

Fig. 11 Transfer curve shift of the top gate AZTO TFT with PL under the +20 V gate bias voltage.

Fig. 12 Transfer characteristics of the top gate AZTO TFT without PL after annealing at  $300^{\circ}$ C.

nealed AZTO TFT without PL are shown in Figs. 12 and 13, respectively. The  $\mu_{\text{FET}}$  of the 300°C annealed top gate AZTO TFT without PL was  $6.2 \text{ cm}^2/\text{Vs}$ . And the shoulders in sub-threshold region and S/S were scarcely improved compared to the 250°C annealed TFT. The shift of  $V_{on}$  under +20 V of gate bias after 14 hrs was 0.7 V as shown in Fig. 13. The bias stability was scarcely improved too. The improvement of electrical properties and stability are considered to be restrictive just by post-annealing. The interface control by the PL was more important to improve the electrical properties and stability than the post annealing. Although the PL thickness was 30 nm, it was enough to protect the active-insulator interface from the contamination. Therefore, the defects degrading electrical characteristics at the active-insulator interface region were supposed to be reduced by the PL deposited with plasma enhanced ALD. Generally, oxygen plasma treatment on oxide thin film may damage the surface and the surface damage can be recovered by post-annealing considerably. In oxide TFTs, the interface defects related oxygen vacancy, hydrogen and carbon may deteriorate the electrical properties significantly. And the active surface should be defective before the PL deposi-

Fig. 13 Transfer curve shift of the top gate AZTO TFT annealed at  $300^{\circ}$ C without PL under the +20 V gate bias voltage.

Fig. 14 AMOLED panel using the top gate AZTO TFT back-plane.

tion because the active layer deposited by room temperature sputtering. It is supposed that the oxygen plasma used in the PL process reduced such defects and the post-annealing at 300°C recovered the oxygen plasma-induced damages sufficiently. The oxygen plasma effect and the post-annealing in combination with the elimination of active patterning process were considered to enhance the electrical performance and stability of the top gate AZTO TFTs.

The transparent AMOLED panel using the top gate AZTO TFT back-plane is shown in Fig. 14. The AMOLED pixel had 2 transistors and 1 capacitor structure, and the AMOLED display specification was 2.5 inch QCIF+ monochrome. The TFT array had staggered type top gate structure, the  $Al_2O_3$  PL, and the  $Al_2O_3$  gate insulator by atomic layer deposition method. The transparency of the AMOLED panel in visible region was more than 55%. Although left side of the AMOLED panel showed many white spots, the image of the input data was clear and bright. The back-plane of the AMOLED panel using the top gate AZTO TFT array showed good electrical performance and stability.

#### 4. Conclusion

We have manufactured novel oxide TFTs with Al<sub>2</sub>O<sub>3</sub>-ZnO- $SnO_2$  (AZTO) active layer which was deposited at room temperature and processed at relatively low temperature. The AZTO layer was deposited by the RF magnetron sputtering which is convenient for large size commercial production. The film deposition at room temperature and the low temperature processing are significant advantages for the fabrication of flexible electronics. The AZTO TFTs with bottom gate structure exhibited good electrical performance in spite of low temperature processing. The 180°C annealed TFT with bottom gate structure exhibited the  $\mu_{\text{FET}}$ of  $10.1 \text{ cm}^2/\text{Vs}$ , the  $V_{\text{on}}$  of 0.9 V, the  $I_{\text{on}}/I_{\text{off}}$  of more than  $10^9$ and the S/S of 0.58 V/dec. However, their bias stability was not enough to apply AMOLED back plane. The AZTO TFT with top gate structure including protective layer showed excellent bias stability as well as good field effect mobility  $(9.5 \text{ cm}^2/\text{Vs})$  and sub-threshold swing (0.15 V/dec). We also fabricated the 2.5 inch AMOLED panel (QCIF+; 176 X 220, MONO) driven by the top gate AZTO TFT. We are developing the optimum process of AZTO TFT fabrication at low temperature below 200°C for better performance. The AZTO TFT is considered to be an excellent candidate for active matrix back-plane of large size flexible displays and electronics with plastic substrates.

### Acknowledgments

This work was supported by IT R&D program of Ministry of Knowledge Economy. [2006-S079-02, Smart window with transparent electronic devices] Authors gratefully acknowledge DONGWOO FINE-CHEM for the support of chemicals and SDT for AMOLED panel driving.

#### References

- J.-H. Lee, D.-H. Kim, D.-J. Yang, S.-Y. Hong, K.-S. Yoon, P.-S. Hong, C.-O. Jeong, H.-S. Park, S.Y. Kim, S.K. Lim, S.S. Kim, K.-S. Son, T.-S. Kim, J.-Y. Kwon, and S.-Y. Lee, "World's largest (15inch) XGA AMLCD panel using IGZO oxide TFT," SID 08 Digest, 42.2, pp.625–628, 2008.

- [2] K.-S. Son, T.-S. Kim, J.-S. Jung, M.-K. Ryu, K.-B. Park, B.-W. Yoo, J.-W. Kim, Y.-G. Lee, J.-Y. Kwon, S.-Y. Lee, and J.-M. Kim, "4 inch QVGA AMOLED driven by the threshold voltage controlled amorphous GIZO (Ga<sub>2</sub>O<sub>3</sub>-In<sub>2</sub>O<sub>3</sub>-ZnO) TFT," SID 08 Digest, 42.4L, pp.633–636, 2008.

- [3] E. Fortunato, P. Barquinha, A. Pimentel, A. Gonsalves, A. Marques, L. Pereira, and R. Martins, "Fully transparent ZnO thin-film transistor produced at room temperature," Adv. Mater., vol.17, pp.590–594, 2005.

- [4] P. Barquinha, A. Pimentel, A. Marques, L. Pereira, R. Martins, and E. Fortunato, "Influence of the semiconductor thickness on the electrical properties of transparent TFTs based on indium zinc oxide," J. Non-Cryst. Solids, vol.352, pp.1749–1752, 2006.

- [5] H.Q. Chiang, J.F. Wager, R.L. Hoffman, J. Jeong, and D.A. Keszler, "High mobility transparent thin-film transistors with amorphous zinc tin oxide channel layer," Appl. Phys. Lett., vol.86, 013503, 2005.

- [6] K. Nomura, A. Takagi, T. Kamiya, H. Ohta, M. Hirano, and H. Hosono, "Amorphous oxide semiconductors for high-performance

flexible thin-film transistors," Jpn. J. Appl. Phys., vol.45, pp.4303–4308, 2006.

- [7] H. Kumomi, K. Nomura, T. Kamiya, and H. Hosono, "Amorphous oxide channel TFTs," Thin Solid Films, vol.516, pp.1516–1522, 2008.

- [8] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thinfilm transistors using amorphous oxide semiconductors," Nature, vol.432, pp.488–492, 2004.

- [9] D.-H. Cho, S. Yang, C. Byun, J. Shin, M.K. Ryu, S.-H. Ko Park, C.-S. Hwang, S.M. Chung, W.-S. Cheong, S.M. Yoon, and H.Y. Chu, "Transparent Al-Zn-Sn-O thin film transistors prepared at low temperature," Appl. Phys. Lett., vol.93, 142111, 2008.

- [10] P.F. Carcia, R.S. McLean, M.H. Reilly, and G. Nunes, Jr., "Transparent ZnO thin-film transistor fabricated by rf magnetron sputter," Appl. Phys. Lett., vol.82, no.7, pp.1117–1119, 2003.

- [11] D.-H. Cho, S. Yang, C. Byun, J.-I. Lee, C.-S. Hwang, S.-H. Ko Park, H.Y. Chu, and K.I. Cho, "Novel oxide thin film transistors for transparent AMOLED," Digest of IMID'08, 25-3, pp.1101–1104, 2008.

- [12] H. Hosono, "Ionic amorphous oxide semiconductors: Material design, carrier transport, and device application," J. Non-Cryst. Solids, vol.352, pp.851–858, 2006.

- [13] H. Hosono, K. Nomura, Y. Ogo, T. Uruga, and T. Kamiya, "Factors controlling electron transport properties in transparent amorphous oxide semiconductors," J. Non-Cryst. Solids, vol.354, pp.2796– 2800, 2008.

**Doo-Hee Cho** received the Ph.D. degree in materials chemistry from Kyoto University in 1996. He worked in area of the float glass manufacturing, and LOW-E coating on float glass at the glass research center Keumkang Chemical Co. during the period from 1996 to 1998. Since he joined Electronics and Telecommunications Research Institute in 1998, he has been involved in specialty optical fiber material and transparent oxide TFT research. His major research interests include oxide TFT and transparent dis-

play devices.

Sang-Hee Ko Park received the B.S. and M.S. in chemistry education department from Seoul National University in 1987 and 1989, and the Ph.D. degree in chemistry department from the University of Pittsburgh in 1997. Her dissertation work included the mechanism of synthesis of organometallic compounds. After graduation, she joined the Electronics and Telecommunications Research Institute, Korea in 1998, where she had worked on the fabrication of electrolumescnet display, phosphor, pas-

sivation of organic light emitting diodes, and material development for the flat panel display using ALD. She has been working with oxide TFT.

Shinhyuk Yang received the M.E. degree in electronics engineering from Dankook University in 2008. He joined Electronics and Telecommunications Research Institute in 2007. He has been focusing on research and development of stability characteristics of oxide TFT and flexible device composed of oxide/organic materials. He is now candidate for Ph.D. in Kyoung-Hee University.

the M.S. degrees in electrical and computer engineering from Hanyang University, Seoul, Korea, in 2002 and 2007, respectively. In

2007, he joined Transparent Display Team,

ETRI(Electronics and Telecommunications Re-

search Institute), Daejeon, Korea. His research

interests include the transparent electronics and

driving methods, circuits for flat panel displays.

Chunwon Byun

received the M.S. and Sung Min Yoon Ph.D. in Department of Applied Electronics from Tokyo Institute of Technology (TIT), Tokyo, Japan, 1997 and 2000, respectively. His Ph.D. work focused on the fabrication of an adaptive-learning neuron-chip using ferroelectric memory device. Currently, he is a Senior Research Engineer at Electronics and Telecommunications Research Institute (ETRI), Korea. He was awarded the JSAP Award for Research Paper Presentation in 1999, and SSDM Young

Researcher Award in 1999, the Teshima Prize in 2000, and Best presentation Award at E-MRS Spring Meeting in 2008.

Hve Yong Chu received the B.S. and M.S. degrees in physics from Kyung-Hee University in 1987 and 1989, respectively. She joined the Electronics and Telecommunications Research Institute, Korea in 1989. She earned Ph.D. degree in information display from Kyung-Hee University in 2008. Her current research interests include novel device architectures in organic light emitting devices.

received the B.S. and

Min Ki Ryu received the Ph.D. degree in physics from Pusan National University in 2004. Since he joined Electronics and Telecommunications Research Institute in 2005, he has been involved in memory materials and transparent conductive oxide research. His major research interests include oxide TFT and transparent display devices.

Jeong-Ik Lee received the B.S., M.S., and the Ph.D. degrees in chemistry from Korea Advanced Institute of Science and Technology (KAIST) in 1992, 1994 and 1997, respectively. After graduation, he joined IBM Almaden Research Center, San Jose, CA, USA as a post-doc, where he worked on organic light emitting materials. He moved to the Electronics and Telecommunications Research Institute, Korea in 1999 and has been continuing his research on organic light emitting devices for display and lighting

applications.

**Chi-Sun Hwang** received the Master degree in physics from Korea Institute of Science and Technology, and Ph.D. degree in the same institute in 1996. He worked in area of the MOSFET at Hyudai Electronics Co., Ltd. from 1996 to 1998. Since he joined Electronics and Telecommunications Research Institute in 1998, he has been involved in FED and transparent oxide TFT research. His major research interests include oxide TFT and transparent display devices.

Kyoung Ik Cho received the B.S. degree in Materials Science from Ulsan Institute of Technology in 1979, and the M.S. and Ph.D. degrees in Material Science and Engineering from Korea Advanced Institute of Science and Technology, in 1981 and 1991, respectively. He joined the Electronics and Telecommunications Research Institute (ETRI) in 1981. He has been working on the development of advanced display devices, and new electronic devices and materials. His current research interests include oxide TFT

and transparent display, and flexible electronic devices.